In the last post we have discussed the setup and hold timings when there is a skew in the data path. In this section we will discuss the case when there is a skew in the clock path.

In the last post we have discussed the setup and hold timings when there is a skew in the data path. In this section we will discuss the case when there is a skew in the clock path.

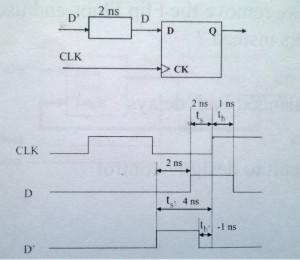

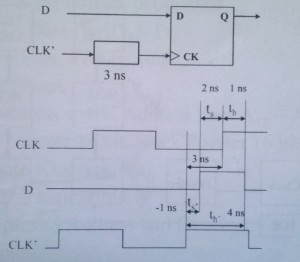

As shown in the diagram there is a 3 ns skew in the clock path. Assume that there is no skew in data path. We have a pin at CLK’ that suffers a delay of 3 ns before it reaching the CK port of the particular flip flop. We would like to know the relation of the data setup and hold time at D with respect to CLK’ where we have control.

The original clock(CLK) is shown and has a setup time of 2 ns and hold time of 1 ns with respect to D. The new reference clock CLK’ is appearing earlier to CLK by 3 ns. If you refer to the waveforms you can see that, the data at D is setting up after the active edge of CLK’. So the setup time which was earlier 2ns is now -1 ns (2ns -3ns) which is negative. Now for the hold time, the data has to be stable for an additional 3 ns after the active edge of CLK’ resulting a hold time of 4 ns.

So this means that if there is a skew in the clock path, the setup time is reduced and the hold time is increased, both by the delay in the clock path. In this case the setup time can be negative which means that with respect to CLK’, the data is setup after the active clock edge.

Point to note:

- When there is a delay ‘t’ in the path to clock input, the setup time with respect to new reference point CLK’ is decreased by t and hold time is increased by t.

- In this case the setup time can take a negative value. A setup time of -t means that at point CLK’ the data at D can be setup ‘t’ time after the active clock edge.

- Setup time is defined as time before clock, the data has to be setup. So for setup time positive value is going backward from the clock edge and negative value means it is forward from the clock. For hold time, the reverse case applies.

Reference: NPTEL Lecture series on Digital System design with PLDs and FPGAs by Kuruvilla Varghese, DESE, IISc Bangalore