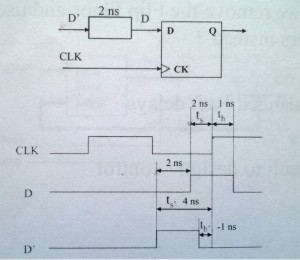

We know that for a flip flop, the setup time and the hold time is specified at the input D as shown in the diagram. The timing parameters states that, with respect to the active clock(CLK) edge, there is a setup time (ts = 2ns) before which the data has to be setup and there is a hold time (th = 1ns) for which the data has to be held some time after the clock edge.

We know that for a flip flop, the setup time and the hold time is specified at the input D as shown in the diagram. The timing parameters states that, with respect to the active clock(CLK) edge, there is a setup time (ts = 2ns) before which the data has to be setup and there is a hold time (th = 1ns) for which the data has to be held some time after the clock edge.

Here in this waveform, the data is changing from 0 to 1, 2 ns (ts) before the active clock edge and remain high for 2 ns up to the clock edge and 1 ns more after the clock edge and then it changes.

But many at a times we may take the input at a pin D’ on a chip, like a wire is going from a pin through a buffer and reaches at D. So there could be additional delays in the data path. Here in this case point D’ incur a delay of 2 ns w.r.t D, meaning that when you give a data at D’, it appears at D after 2 ns delay. When you supply a clock (assume CLK has no delay) we would like to know what is the setup time and hold time w.r.t the point D’, because we have control over this point only, we are supplying data from outside at this point and we are not worried about the setup and hold time at the point D since that doesn’t help us because there is an additional 2 ns delay.

what is the new setup time at D’ ?

With respect to CLK, the setup time has increased because the data at D’ has to be setup 4 ns (old 2ns(ts) + 2ns data path delay) before the active clock edge. So the data path delay 2 ns is added to the setup time and setup time has increased.

What is the new hold time at D’?

Hold time is 1 ns towards left of the active clock edge. Remember Setup time is defined as the time before the active clock edge, the data has to setup and the Hold time is defined as the time for which the data has to to be held after the active clock edge. But here in this case, the data is removed before the active clock edge (normally we remove data after the active clock edge) and so the hold time become -ve and is -1 ns (old 1ns (th) – 2 ns data path delay). When the hold time become -ve in the opposite direction, it means that you can remove the data at D’ even before the active clock edge.

Points to note

- When there is a delay ‘t’ in the path to D input, the setup time w.r.t new reference point D’ is increased by t and hold time is decreased by t.

- In this case hold time can take a -ve value. A hold time of -t means at point D’, the data can be removed or changed ‘t’ time before the active clock edge

Reference: NPTEL Lecture series on Digital System design with PLDs and FPGAs by Kuruvilla Varghese, DESE, IISc Bangalore